Standard Performance Evaluation Corporation (SPEC)

# Server Efficiency Rating Tool (SERT) Design Document 1.1.1

7001 Heritage Village Plaza, Suite 225 Gainesville, VA 20155, USA

**SPECpower Committee**

# Table of Contents

| 1.                | Int                          | roduction                                         | 7                           |

|-------------------|------------------------------|---------------------------------------------------|-----------------------------|

| 1.1               | L. S                         | Summary                                           | .7                          |

| 1.2               | 2. 4                         | About SPEC                                        |                             |

| -                 | 1.2.1.                       |                                                   |                             |

| -                 | 1.2.2.                       | SPEC Membership                                   | 8                           |

| 2.                | SE                           | RT's Scope and Goals                              | 8                           |

| 2.1               | L. C                         | Dverview Summary                                  | 8                           |

| 2.2               | 2. 5                         | SERT's Differences from Conventional Benchmarks   | .9                          |

| 2.3               | B. S                         | Sockets and Nodes                                 | .9                          |

| 2.4               | I. S                         | Scaling                                           | .9                          |

| 2.5               | 5. S                         | Server Options and Expansion Capabilities         | 10                          |

| 2.6               | 5. F                         | Redundancy                                        | 10                          |

| 2.7               | 7. F                         | Run Time                                          | 10                          |

| 2.8               | B. C                         | Customer Relevant Measurements                    | 10                          |

| 2.9               | ). I                         | mplementation Languages                           | 10                          |

| 2.1               | L <b>O.</b>                  | Load Levels                                       | 11                          |

| 2.1               | 1.                           | Platforms                                         | 11                          |

| 2.1               | L <b>2</b> .                 | Platform Addition Requirements                    |                             |

| 2                 | 2.12.1                       |                                                   |                             |

|                   | 2.12.2                       |                                                   |                             |

|                   | 2.12.3                       |                                                   |                             |

|                   | 2.12.4                       |                                                   |                             |

|                   | 2.12.5                       |                                                   |                             |

|                   | 2.12.6                       |                                                   |                             |

|                   | 2.12.7                       |                                                   |                             |

| 2.1               | L <b>3</b> .                 | Incremental Changes to Accepted Environments      |                             |

| 2                 | 2.13.1                       |                                                   |                             |

| 2                 | 2.13.2                       | 2. Acceptance for Different Revisions of the SERT | 14                          |

|                   |                              |                                                   |                             |

| 3.                |                              | e SERT Architecture                               | 15                          |

| <i>3.</i><br>3.1  |                              | e SERT Architecture                               | 15                          |

| •                 | L. E                         |                                                   | 15<br>15                    |

| 3.1               | l. E<br>2. S                 | Environment Overview                              | <i>15</i><br>15<br>16       |

| 3.1<br>3.2        | L. E<br>2. S<br>3. N         | Environment Overview                              | <i>15</i><br>15<br>16<br>17 |

| 3.1<br>3.2<br>3.3 | L. E<br>2. S<br>8. \<br>I. \ | Environment Overview                              | 15<br>15<br>16<br>17<br>17  |

| 4.2.              | Ten                | nperature Sensor Specifications1 | 19 |

|-------------------|--------------------|----------------------------------|----|

| 4.3.              | Pov                | ver Analyzer Requirements1       | 19 |

| 4.4.              | SPE                | C PTDaemon2                      | 20 |

| 4.5.              | Sup                | ported and Compliant Devices2    | 20 |

| <b>4.6.</b><br>4. | <b>Pov</b><br>6.1. | ver Analyzer Setup               |    |

| 4.7.              | DC                 | Line Voltage                     | 20 |

| 5.                |                    | hical User Interface             |    |

|                   | -                  | -                                |    |

| 6.                |                    | ic/Score, Reporting, Logging2    |    |

| 6.1.              | Me                 | tric/Score2                      | 24 |

| 6.2.              | Rep                | orting and Output Files2         | 24 |

| 6.                | 2.1.               | Report Formats                   | 24 |

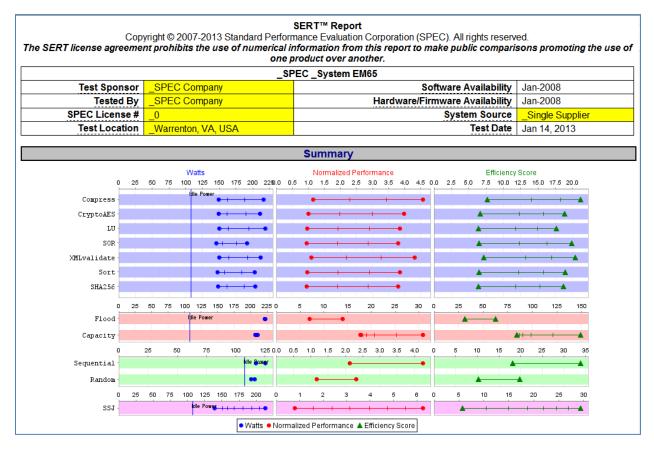

| 6.                | 2.2.               | Sample HTML Report Output        | 25 |

| 6.                | 2.3.               | Sample TXT Report Output         | 26 |

| 6.                | 2.4.               | Score Calculation                | 27 |

| 6.3.              | 32-I               | Bit Results2                     | 27 |

| 6.4.              | Vali               | dation / Verification2           | 28 |

| 6.5.              | Log                | ging2                            | 28 |

| 7.                | Work               | let Design Guidelines            | 29 |

| 7.1.              |                    | ے<br>I Worklets2                 |    |

| 7.2.              |                    | mory Worklets                    |    |

| 7.3.              |                    | Vorklets                         |    |

| -                 | -                  |                                  |    |

|                   | 3.1.               | Network IO Worklets              |    |

|                   | 3.2.               | Storage IO Worklets              |    |

| 7.4.              | Hyb                | orid Worklets                    | 30 |

| 7.5.              | Idle               | Worklet                          | 30 |

| 8.                | Work               | let Details                      | 1  |

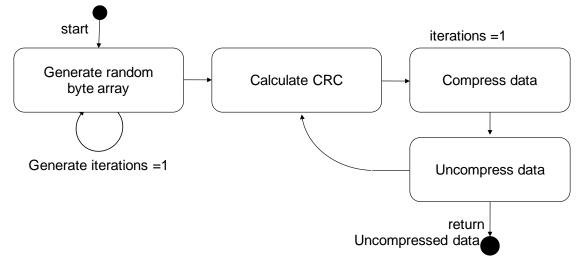

| 8.1.              | CPU                | J Worklet: Compress              | 32 |

| 8.                | 1.1.               | General Description              | 32 |

| 8.                | 1.2.               | Sequence Execution Methods       |    |

| 8.                | 1.3.               | Metric                           |    |

| 8.                | 1.4.               | Required Initialization          | 32 |

| 8.                | 1.5.               | Configuration Parameters         |    |

| 8.                | 1.6.               | Transaction Code                 |    |

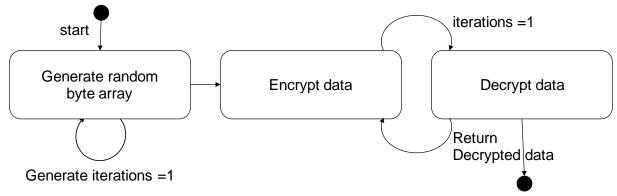

| 8.2.              | CPU                | J Worklet: CryptoAES             |    |

|                   | 2.1.               | General Description              |    |

| -                 | 2.2.               | Sequence Execution Methods       |    |

| -                 | 2.3.               | Metric                           |    |

| -                 | 2.4.               | Required Initialization          |    |

| -                 | 2.5.               | Configuration Parameters         |    |

|                   |                    | -                                |    |

| 8.2.6.  | Transaction Code           |    |

|---------|----------------------------|----|

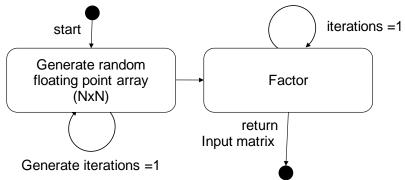

| 8.3. CP | U Worklet: LU              | 34 |

| 8.3.1.  | General Description        | 34 |

| 8.3.2.  | Sequence Execution Methods | 34 |

| 8.3.3.  | Metric                     | 34 |

| 8.3.4.  | Required Initialization    | 34 |

| 8.3.5.  | Configuration Parameters   | 34 |

| 8.3.6.  | Transaction Code           | 34 |

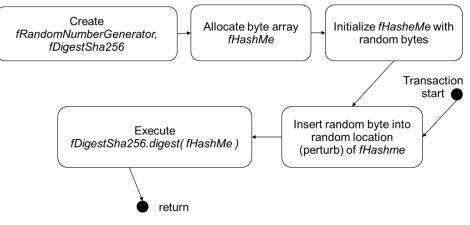

| 8.4. CP | U Worklet: SHA256          | 35 |

| 8.4.1.  | General Description        | 35 |

| 8.4.2.  | Sequence Execution Methods | 35 |

| 8.4.3.  | Metric                     | 35 |

| 8.4.4.  | Required Initialization    | 35 |

| 8.4.5.  | Configuration Parameters   | 35 |

| 8.4.6.  | Transaction Code           | 35 |

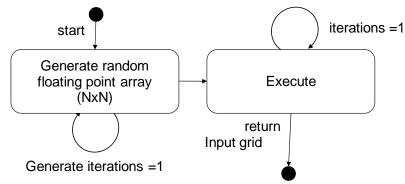

| 8.5. CP | U Worklet: SOR             | 36 |

| 8.5.1.  | General Description        |    |

| 8.5.2.  | Sequence Execution Methods |    |

| 8.5.3.  | Metric                     |    |

| 8.5.4.  | Required Initialization    |    |

| 8.5.5.  | Configuration Parameters   |    |

| 8.5.6.  | Transaction Code           |    |

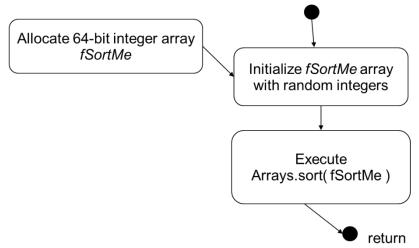

| 8.6. CP | U Worklet: SORT            |    |

| 8.6.1.  | General Description        |    |

| 8.6.2.  | Sequence Execution Methods |    |

| 8.6.3.  | Metric                     |    |

| 8.6.4.  | Required Initialization    |    |

| 8.6.5.  | Configuration Parameters   |    |

| 8.6.6.  | Transaction Code           |    |

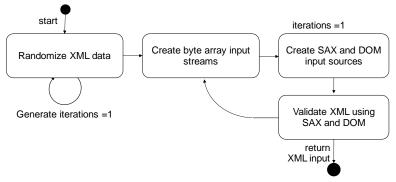

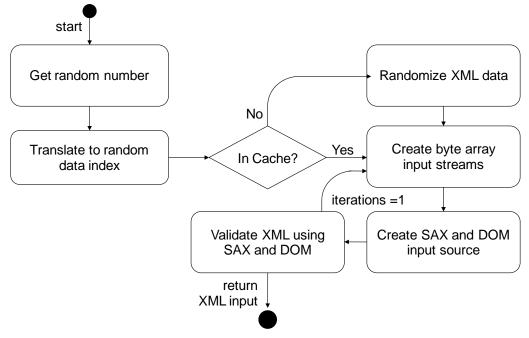

| 8.7. CP | U Worklet: XMLValidate     |    |

| 8.7.1.  | General Description        |    |

| 8.7.2.  | Sequence Execution Methods |    |

| 8.7.3.  | Metric                     |    |

| 8.7.4.  | Required Initialization    |    |

| 8.7.5.  | Configuration Parameters   |    |

| 8.7.6.  | Transaction Code           |    |

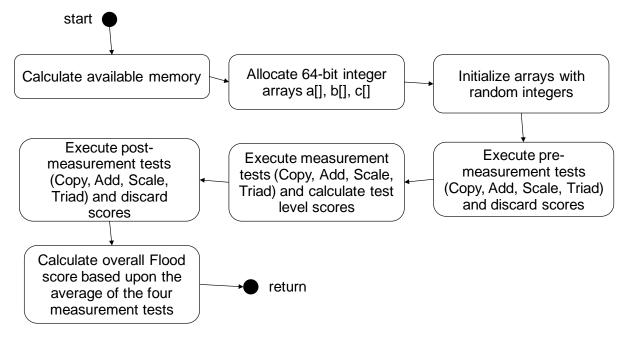

| 8.8. Me | emory Worklet: Flood2      |    |

| 8.8.1.  | General Description        |    |

| 8.8.2.  | Sequence Execution Methods |    |

| 8.8.3.  | Metric                     |    |

| 8.8.4.  | Required Initialization    |    |

| 8.8.5.  | Configuration Parameters   |    |

| 8.8.6.  | Transaction Code           |    |

| 8.9. Me | emory Worklet: Capacity2   |    |

| 8.9.1.  | General Description        |    |

| 8.9.2.  | Sequence Execution Methods |    |

| 8.9.3.  | Metric                     |    |

| 8.9.4.  | Required Initialization    |    |

| 8.                                                                                       | 9.5.                                                                                                  | Configuration Parameters                                                                                                                                                                                                                                                                                                 | 42                            |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 8.                                                                                       | 9.6.                                                                                                  | Transaction Code                                                                                                                                                                                                                                                                                                         | 43                            |

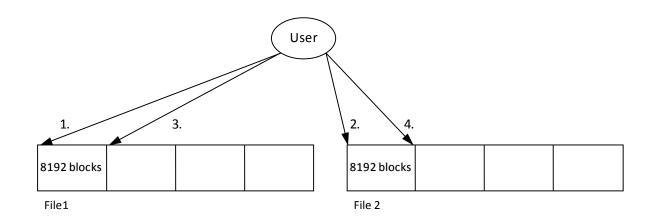

| 8.10                                                                                     | •                                                                                                     | Storage IO Workload                                                                                                                                                                                                                                                                                                      | 11                            |

|                                                                                          | , .<br>10.1.                                                                                          | General Description                                                                                                                                                                                                                                                                                                      |                               |

| -                                                                                        | 10.2.                                                                                                 | Sequence Execution Methods                                                                                                                                                                                                                                                                                               |                               |

| -                                                                                        | 10.2.                                                                                                 | Metric                                                                                                                                                                                                                                                                                                                   |                               |

| -                                                                                        | 10.4.                                                                                                 | Required Initialization                                                                                                                                                                                                                                                                                                  |                               |

|                                                                                          | 10.5.                                                                                                 | Configuration Parameters                                                                                                                                                                                                                                                                                                 |                               |

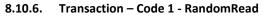

|                                                                                          | 10.6.                                                                                                 | Transaction – Code 1 - RandomRead                                                                                                                                                                                                                                                                                        |                               |

|                                                                                          | 10.7.                                                                                                 | Transaction – Code 1 - RandomWrite                                                                                                                                                                                                                                                                                       |                               |

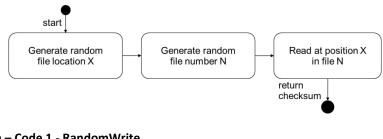

| -                                                                                        | 10.7.                                                                                                 | Transaction – Code 2 – SequentialRead                                                                                                                                                                                                                                                                                    |                               |

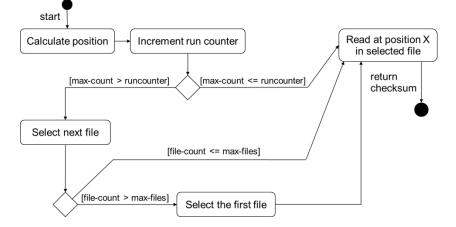

|                                                                                          | 10.9.                                                                                                 | Transaction – Code 2 – SequentialWrite                                                                                                                                                                                                                                                                                   |                               |

|                                                                                          |                                                                                                       |                                                                                                                                                                                                                                                                                                                          |                               |

| 8.11                                                                                     |                                                                                                       | Hybrid Worklet: SSJ                                                                                                                                                                                                                                                                                                      |                               |

| -                                                                                        | 11.1.                                                                                                 | General Description                                                                                                                                                                                                                                                                                                      |                               |

| -                                                                                        | 11.2.                                                                                                 | Sequence Execution Methods                                                                                                                                                                                                                                                                                               |                               |

|                                                                                          | 11.3.                                                                                                 | Metric                                                                                                                                                                                                                                                                                                                   |                               |

| -                                                                                        | 11.4.                                                                                                 | Required Initialization                                                                                                                                                                                                                                                                                                  |                               |

| -                                                                                        | 11.5.                                                                                                 | Configuration Parameters                                                                                                                                                                                                                                                                                                 |                               |

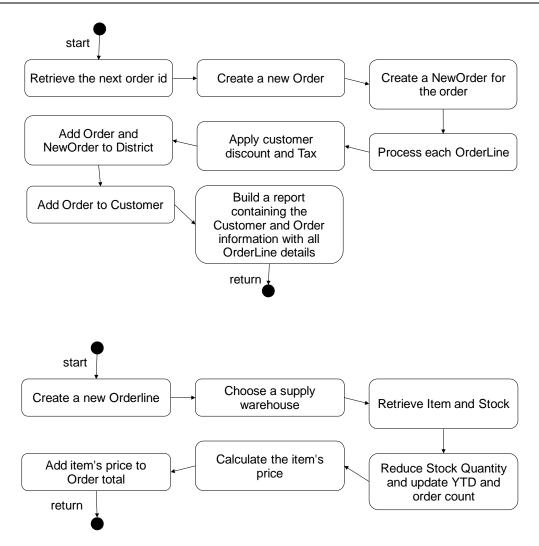

| -                                                                                        | 11.6.                                                                                                 | New Order Transaction                                                                                                                                                                                                                                                                                                    |                               |

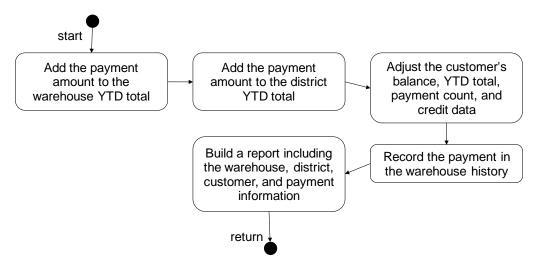

| -                                                                                        | 11.7.                                                                                                 | Payment Transaction                                                                                                                                                                                                                                                                                                      |                               |

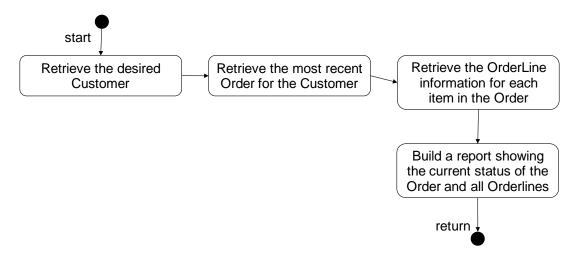

| -                                                                                        | 11.8.                                                                                                 | Order Status Transaction                                                                                                                                                                                                                                                                                                 |                               |

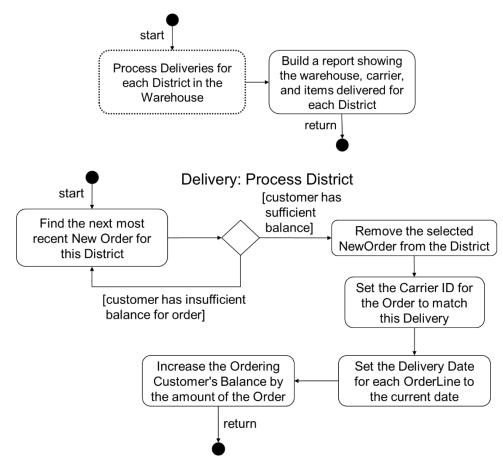

| -                                                                                        | 11.9.                                                                                                 | Delivery Transaction                                                                                                                                                                                                                                                                                                     |                               |

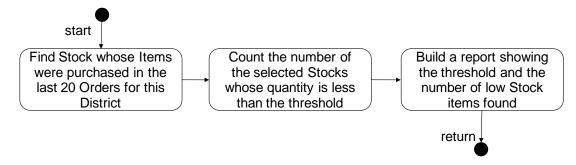

| -                                                                                        | 11.10.                                                                                                |                                                                                                                                                                                                                                                                                                                          |                               |

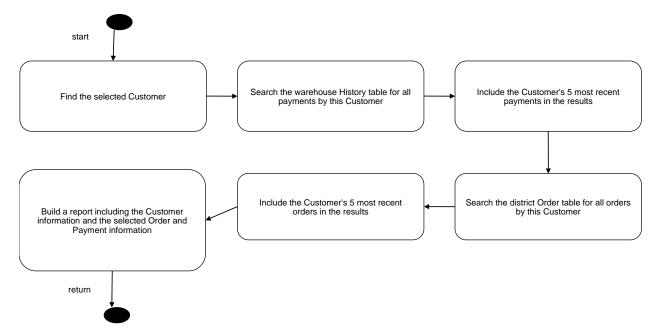

| 8.                                                                                       | 11.11.                                                                                                | Customer Report Transaction                                                                                                                                                                                                                                                                                              | 49                            |

|                                                                                          |                                                                                                       |                                                                                                                                                                                                                                                                                                                          |                               |

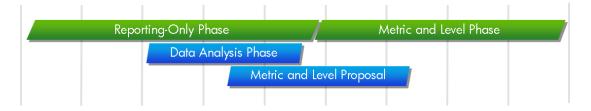

| 9.                                                                                       | Ener                                                                                                  | gy Efficiency Regulatory Programs and the SERT                                                                                                                                                                                                                                                                           | 50                            |

|                                                                                          |                                                                                                       |                                                                                                                                                                                                                                                                                                                          |                               |

| 9.1.                                                                                     |                                                                                                       | easurement                                                                                                                                                                                                                                                                                                               | 50                            |

| <b>9.1.</b><br>9.                                                                        | <b>M</b> e<br>1.1.                                                                                    | easurement<br>Scoring and Metric                                                                                                                                                                                                                                                                                         | <b>50</b>                     |

| <b>9.1.</b><br>9.<br>9.                                                                  | <b>Me</b><br>1.1.<br>1.2.                                                                             | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier                                                                                                                                                                                                                                             | <b>50</b><br>50               |

| <b>9.1.</b><br>9.                                                                        | <b>Me</b><br>1.1.<br>1.2.                                                                             | easurement<br>Scoring and Metric                                                                                                                                                                                                                                                                                         | <b>50</b><br>50               |

| <b>9.1.</b><br>9.<br>9.                                                                  | Me<br>1.1.<br>1.2.<br>SE                                                                              | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier                                                                                                                                                                                                                                             | <b>50</b><br>50<br><b>5</b> 0 |

| 9.1.<br>9.<br>9.<br>9.2.<br>9.3.                                                         | Me<br>1.1.<br>1.2.<br>SE                                                                              | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention                                                                                                                                                                                      | <b>50</b><br>                 |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.                                                       | Ma<br>1.1.<br>1.2.<br>SE<br>Ma<br>Pu                                                                  | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information                                                                                                                                            |                               |

| 9.1.<br>9.<br>9.<br>9.2.<br>9.3.                                                         | Ma<br>1.1.<br>1.2.<br>SE<br>Ma<br>Pu                                                                  | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention                                                                                                                                                                                      |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.                                                       | Ma<br>1.1.<br>1.2.<br>SE<br>Ma<br>Pu<br>Ge                                                            | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information                                                                                                                                            |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.                                               | Ma<br>1.1.<br>1.2.<br>SE<br>Ma<br>Pu<br>Ge<br>Ac                                                      | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information<br>eneral Availability (GA)<br>credited, Independent Laboratory                                                                            |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.<br>9.6.<br>9.7.                               | Ma<br>1.1.<br>1.2.<br>Ma<br>Pu<br>Ge<br>Ac<br>Su                                                      | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information<br>eneral Availability (GA)<br>credited, Independent Laboratory<br>pply Voltage Tolerance                                                  |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.<br>9.6.                                       | Ma<br>1.1.<br>1.2.<br>Ma<br>Pu<br>Ge<br>Ac<br>Su                                                      | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information<br>eneral Availability (GA)<br>credited, Independent Laboratory                                                                            |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.<br>9.6.<br>9.7.                               | Ma<br>1.1.<br>1.2.<br>Ma<br>Pu<br>Ge<br>Ac<br>Su<br>Logi                                              | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information<br>eneral Availability (GA)<br>credited, Independent Laboratory<br>pply Voltage Tolerance                                                  |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.<br>9.6.<br>9.7.<br>10.                        | Ma<br>1.1.<br>1.2.<br>Ma<br>Pu<br>Ge<br>Ac<br>Su<br>Logi                                              | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information<br>eneral Availability (GA)<br>credited, Independent Laboratory<br>pply Voltage Tolerance                                                  |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.<br>9.6.<br>9.7.<br>10.                        | Ma<br>1.1.<br>1.2.<br>SEI<br>Ma<br>Pu<br>Ge<br>Ac<br>Su<br><i>Logi</i>                                | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information<br>eneral Availability (GA)<br>credited, Independent Laboratory<br>pply Voltage Tolerance<br>stics<br>Future Enhancement Ideas<br>Worklets |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.<br>9.6.<br>9.7.<br>10.<br>10.1<br>10.1        | Ma<br>1.1.<br>1.2.<br>SEI<br>Ma<br>Pu<br>Ge<br>Ac<br>Su<br>Logi                                       | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information<br>eneral Availability (GA)<br>credited, Independent Laboratory<br>pply Voltage Tolerance<br>stics<br>Future Enhancement Ideas             |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.<br>9.6.<br>9.7.<br>10.<br>10.1<br>10.1        | Ma<br>1.1.<br>1.2.<br>SE<br>Ma<br>Pu<br>Ge<br>Ac<br>Su<br>Logi<br>1.<br>1.1.1.<br>0.1.1.<br>0.1.3.    | easurement<br>Scoring and Metric<br>Configuration Power/Performance Modifier<br>RT Binaries and Recompilation<br>anual Intervention<br>blic Usage of SERT Results Information<br>eneral Availability (GA)<br>credited, Independent Laboratory<br>pply Voltage Tolerance<br>stics<br>Future Enhancement Ideas<br>Worklets |                               |

| 9.1.<br>9.<br>9.2.<br>9.3.<br>9.4.<br>9.5.<br>9.6.<br>9.7.<br>10.<br>10.1<br>10.<br>10.1 | Ma<br>1.1.<br>1.2.<br>SE<br>Ma<br>Pu<br>Ge<br>Ac<br>Su<br>Logi:<br>1.1.1.<br>0.1.1.<br>0.1.3.<br>2. I | easurement                                                                                                                                                                                                                                                                                                               |                               |

SVN Revision: 2000

SVN Date: 2016/01/13 02:26:29

# 1. Introduction

# 1.1. Summary

The Server Efficiency Rating Tool (SERT)<sup>TM</sup> was created by Standard Performance Evaluation Corporation (SPEC), the world's leading organization for benchmarking expertise, at the request of the US Environmental Protection Agency. It is intended to measure server energy efficiency, initially as part of the second generation of the US Environmental Protection Agency (EPA) ENERGY STAR for Computer Servers program. Designed to be simple to configure and use via a comprehensive graphical user interface, the SERT uses a set of synthetic worklets to test discrete system components such as memory and storage, providing detailed power consumption data at different load levels. Results are provided in both machine- and human-readable forms, enabling automatic submission to government-sponsored certification programs as well as both summary and detail reports for use by potential customers.

This public draft outlines the design of the SERT for public review; please visit <u>http://www.spec.org/sert/docs/SERT-Design\_Document.pdf</u> for the latest updates.

# 1.2. About SPEC

The Standard Performance Evaluation Corporation (SPEC) was formed by the industry in 1988 to establish industry standards for measuring compute performance. SPEC has since become the largest and most influential benchmark consortium world-wide. Its mission is to ensure that the marketplace has a fair and useful set of metrics to analyze the newest generation of IT equipment.

The SPEC community has developed more than 30 industry-standard benchmarks for system performance evaluation in a variety of application areas and has provided thousands of benchmark licenses to companies, resource centers, and educational institutions globally. Organizations using these benchmarks have published more than 20,000 peer-reviewed performance reports on SPEC's website (<u>http://www.spec.org/results.html</u>).

SPEC has a long history of designing, developing, and releasing industry-standard computer system performance benchmarks in a range of industry segments, plus peer-reviewing the results of benchmark runs. Performance benchmarking and the necessary work to develop and release new benchmarks can lead to disagreements among participants. Therefore, SPEC has developed an operating philosophy and range of normative behaviors that encourage cooperation and fairness amongst diverse and competitive organizations.

The increasing demand for energy-efficient IT equipment has resulted in the need for power and performance benchmarks. In response, the SPEC community established SPECpower, an initiative to augment existing industrystandard benchmarks with a power/energy measurement. Leading engineers and scientists in the fields of benchmark development and energy efficiency made a commitment to tackle this task. The development of the first industry-standard benchmark that measures the power and performance characteristics of server-class compute equipment began on January 26 2006. In December of 2007, SPECpower\_ssj2008 was released, which exercises the CPUs, caches, memory hierarchy, and the scalability of shared memory processors on multiple load-levels. The benchmark runs on a wide variety of operating systems and hardware architectures. In version 1.10, which was released on April 15 2009, SPEC augmented SPECpower\_ssj2008 with multi-node support (e.g., blade-support). Several enhancements and code changes to all benchmark components, documentation updates, and run and reporting rules enhancements were included in version 1.11, released September 13, 2011 and version 1.12, released March 30, 2012.

#### **1.2.1.** SPEC's General Development Guidelines

SPEC's philosophy and standards of participation are the basis for the development of the SERT. The tool was been developed cooperatively by a committee representing diverse and competitive companies. The following points guide the committee in the development of a tool that will be useful and widely adopted by the industry:

• Decisions are reached by consensus. Motions require a qualified majority to carry.

- Decisions are based on reality. Experimental results carry more weight than opinions. Data and demonstration overrule assertion.

- Fair benchmarks allow competition among all industry participants in a transparent market.

- Tools and benchmarks should be architecture-neutral and portable.

- All who are willing to contribute may participate. Wide availability of results on the range of available solutions allows the end user to determine the appropriate IT equipment.

Similar guidelines have resulted in the success and wide use of SPEC benchmarks in the performance and power/performance industry and are essential to the success of the SERT.

#### 1.2.2. SPEC Membership

SPEC membership is open to any interested company or entity. The members and associates of SPEC's Open System Group (OSG) are entitled to licensed copies of all released OSG benchmarks and tools as well as unlimited publication of results on SPEC's public website. An initiation fee and annual fees are due for members. Nonprofit organizations and educational institutions have a reduced annual fee structure. Further details on membership information can be found on <u>http://www.spec.org/osg/joining.html</u> or requested at <u>info@spec.org</u>. Also a current list of SPEC members can be found here: <u>http://www.spec.org/spec/membership.html</u>.

# 2. SERT's Scope and Goals

The current scope of the EPA's Energy Star Program for Servers includes servers with 1-4 processor sockets and blade technologies of similar scope. A design goal of the SERT is to accommodate these and larger technologies.

Among the issues involved with support of larger systems are the overall capacity of the system to complete work, and the ability to design a workload that scales with the inclusion of additional processors, memory, network interface cards, disk drives, etc. Different workload characteristics are required to demonstrate effectiveness for each of these components. Providing a workload that fairly represents their presence while not unfairly representing their absence is a challenge. These issues are more prevalent with larger systems that have more expansion capabilities than smaller servers.

For these areas where it is concluded that the tool does not adequately represent the value of a component compared to its power requirements, the tool will be designed to accommodate the inclusion of "Configuration Power/Performance Modifiers".

# 2.1. Overview Summary

The following table summarizes some of the design goals that the SERT will and will not provide:

| IS                                                  | IS NOT                                                               |

|-----------------------------------------------------|----------------------------------------------------------------------|

| A Rating Tool for overall energy efficiency         | A Benchmark nor a Capacity Planning Tool                             |

| A Measuring Tool for power, performance, and inlet- | A Measuring Tool for Airflow, Air pressure, outlet-                  |

| temperature                                         | temperature                                                          |

| A general compute-environment measure               | A specific application, JVM, or special purpose                      |

|                                                     | benchmark measure                                                    |

| Supporting AC-powered servers                       | Able to support DC-powered servers (See Section 4.7)                 |

| Used in single Operating System (OS) instance per   | Intended to stress virtualization hypervisor technology <sup>1</sup> |

| server environments                                 |                                                                      |

| An Energy Efficiency Rating Tool                    | A Marketing Tool                                                     |

| Planned to be architecture- and OS- neutral         | Implemented on architecture and/or OS environments                   |

|                                                     | where insufficient resource has been volunteered to                  |

|                                                     | accomplish development, testing, and support.                        |

<sup>&</sup>lt;sup>1</sup> SERT, as a first-order approximation tool, is not designed to evaluate the impacts of virtualized environments

# **2.2. SERT's Differences from Conventional Benchmarks**

Performance and energy efficiency benchmarks tend to focus on capabilities of computer servers in specific business models or application areas. The SERT is focused on providing a first order of approximation of energy efficiency across a broad range of application environments.

- The absolute score is less relevant for the end user, because it will not reflect specific application capabilities.

- A rating tool that provides a pass-fail or a [Level 1/Level 2/Level 3] rating is a better fit for energyefficiency regulatory programs than a typical benchmark result with multiple digits of precision in the metric.

- Marketing of the absolute scores will be disallowed in order to encourage more participation in the program.

Benchmarks tend to focus on optimal conditions, including tuning options to customize the configuration and software to the application of the benchmark business model. The need to achieve competitive benchmark results often causes significant investment in the benchmark process. The SERT is designed to be more economical and easier to use, requiring minimal equipment and skills through:

- Highly automated processes and leveraging existing SPEC methods

- Focused predetermined settings for the server

- Being free from super-tuning

Where a benchmark represents a fixed reference point, regulatory programs are designed to foster continuous improvement, with thresholds for success rising as the industry progresses. The SERT will be designed to match this paradigm, including:

- Quick adoption of new computing technologies

- Rapid turn-around for tool version updates

# 2.3. Sockets and Nodes

The SERT 1.0.0 is designed to be scalable and will be tested up to a maximum of 8 sockets and a maximum of 64 nodes (limited to a set of homogenous servers or blade servers). The server under test (SUT) may be a single standalone server or a multi-node set of servers. A multi-node SUT will consist of server nodes that cannot run independently of shared infrastructure such as a backplane, power-supplies, fans, or other elements. These shared infrastructure systems are commonly known as "blade servers" or "multi-node servers". Only identical servers are allowed in a multi-node SUT configuration.

# 2.4. Scaling

Since the server efficiency rating of a given server is the primary objective of the SERT, one of the main design goals for the tool is to be able to scale the performance on the system in proportion to the system configuration. As more components (processors, memory, and disk storage) are added to the server, the workloads should utilize the additional resources so that the resultant performance is higher when compared to the performance on the same server with a lesser configuration. Similarly, for a given server, when the components are upgraded with faster counterparts, the performance should scale accordingly. This is a very important aspect of the tool since adding and upgrading components typically increase the total power consumed by the server, which will affect the overall efficiency result of the server. Creating a tool that scales performance based on the number/speed of CPUs is most readily achievable – for the other components, the complexity of implementing such a tool increases substantially.

While the SERT will be designed to scale performance with additional hardware resources of the SUT, the SUT itself may not be able to sustain higher performance if there are performance bottlenecks in system components unrelated to the added hardware. In such cases, the addition of components to the SUT will normally result in

higher power consumption without a commensurate increase in performance. It is also possible that the workload mix that is defined for smaller systems will not scale well when examining larger systems.

### **2.5.** Server Options and Expansion Capabilities

A server may have many optional features that are designed to increase the breadth of applications. These features not only require additional power, but also require more capacity in the power supplies and cooling system. Some of the SERT workload components will be designed to demonstrate the enhanced capabilities that these features provide. However, while the tool needs to credit these capabilities for the expanded workloads that they will accommodate, it cannot penalize efficient servers that are not designed with substantial expansion options. A balance must be struck between providing enhanced ratings for enhanced configurations and avoiding easy qualification of servers by simply adding features that may not be needed in all situations.

The SERT's goal is to avoid unnecessarily penalizing servers that are designed for low expandability, while crediting servers with greater expandability. For example, a configuration with four IO adapters in PCI slots may execute the workload more effectively than a configuration with only one such adapter. On the other hand, it may only run the workload as effectively as a configuration with two network adapters. Because the configuration with four adapters may run some real workloads more effectively than configurations with only two adapters, the regulatory program may elect to allow for some form of "Configuration Power/Performance Modifier" to provide credit for the power infrastructure needed to support the additional PCI slots.

The tool will be designed and tested to ensure that, should "Configuration Power/Performance Modifier" credits be included, the tool will accommodate them.

# 2.6. Redundancy

Many servers have redundancy built in for power supplies and cooling fans. Some servers include different levels of redundancy for memory, disk, and even processors. A design goal is to include accommodation for redundant components via Configuration Power/Performance Modifier, although no specific tests are planned for energy measurement under fault tolerant conditions when one of a redundant set of components is disabled.

# 2.7. Run Time

The right balance between high repeatability of the results, high sub-system coverage, and low resource allocation is desirable. The target run time is around five hours.

# **2.8. Customer Relevant Measurements**

To provide results that are representative of a customer environment, the goal is to test systems in an "asshipped" state. Unless otherwise specified by the Energy Efficiency Regulatory Program that is including the use of the SERT in its evaluation protocol, power management settings for the SUT will be assumed to be the default settings that are shipped with the SUT. Because of the variety of functions that are stressed by the various workloads within the SERT, it is anticipated that some performance tuning will be required to obtain consistent and customer-relevant results. No super-tuning will be allowed. SPEC will host a site with processor vendordefined JVM tuning and flag options. Per workload (see section 3.3 for the SERT definition of a workload), only one set of JVM tuning flags per OS/JVM/micro-architecture configuration (e.g. Windows Server R2/Oracle HotSpot/AMD x86) may be used. For a valid SERT result, the JVM count is user defined. Other changes will cause the run to be non-compliant. The SERT will launch the JVM within the tool to restrict additional tuning.

# 2.9. Implementation Languages

The main body of code is in written in Java in order to lower the burden of cross-platform support. The framework is designed to accommodate other language implementations as well.

# 2.10. Load Levels

The SERT implements our concept of multiple load levels per worklet. The detail load levels can be found in worklet section (see section 8).

# 2.11. Platforms

The SERT 1.0.0 will be implemented for and is planned to be tested on the following platform/OS/JVM combinations (64 bit only), pending resources. In some cases, SPEC recommend the use of more than one JVM, where more than one JVM is generally available and selecting one may unfairly penalize a specific processor architecture or operating system.

| HW Platform                         | OS                                 | MVL                                                              |

|-------------------------------------|------------------------------------|------------------------------------------------------------------|

| x86 - AMD                           | Windows Server 2008 R2             | IBM J9 Java Runtime Environment<br>Java HotSpot 64-Bit Server VM |

| x86 - AMD                           | Red Hat EL 6.2<br>SUSE SLES 11 SP2 | IBM J9 Java Runtime Environment<br>Java HotSpot 64-Bit Server VM |

| x86 - Intel                         | Windows Server 2008 R2             | IBM J9 Java Runtime Environment<br>Java HotSpot 64-Bit Server VM |

| x86 - Intel                         | Red Hat EL 6.2<br>SUSE SLES 11 SP2 | IBM J9 Java Runtime Environment<br>Java HotSpot 64-Bit Server VM |

| POWER - IBM                         | AIX                                | IBM J9 Java Runtime Environment                                  |

| POWER - IBM                         | Red Hat EL 6.2<br>SUSE SLES 11 SP2 | IBM J9 Java Runtime Environment                                  |

| ARMv7 Cortex-A9<br>ARMv7 Cortex-A15 | Ubuntu 12.04<br>Ubuntu 13.04       | Oracle Java HotSpot VM                                           |

Note: OS refers to versions (service pack and patch levels) that are current at the SERT release.

Each row in the above table has a designated Environment Owner/Sponsor within SPEC for the purpose of defining architecture-specific parameters that will be used for valid SERT measurements. Individuals or corporations who are interested in expanding this list are encouraged to join SPEC (see section 1.2) and contribute to SPEC's OSG Power subcommittee as outlined in the next section.

# 2.12. Platform Addition Requirements

SPEC would welcome the addition of other Platform/OS/JVM combinations. Support for additional Platform/OS/JVM combinations requires active participation from the interested parties (Environment Sponsor). The inclusion of a JVM is dependent on an agreement from the JVM provider for unrestricted use of their JVM for the SERT. Companies dedicating additional resources to the SPECpower committee for development of the SERT would relax the schedule constraints.

Required Environment Sponsor commitment:

- Provide substantial initial testing and share test results with the SPECpower Committee, to ensure that the SERT is functioning as expected for the target environment. At the Environment Sponsor's discretion, the test results may be presented as measured or in normalized form.

- Develop a list of recommended tuning parameters that are comparable to parameters designated for other environments and that will be used for all official SERT measurements.

- Recommend documentation changes associated with the environment, including, but not limited to instructions for Storage Worklet cache use, setting huge pages, and descriptive wording, as appropriate

- Provide ongoing testing for any times when enhancements are made to the SERT or when there is a question as to the functionality of the SERT in the target environment.

- Provide technical support in the event that a SERT licensee has a problem running in the environment which cannot be resolved by the SPEC support staff or the current OSG Power Support liaison.

- Participate in SPECpower Committee follow-on work as they examine options for enhancing the SERT product and for generating metrics using the SERT.

- Ensure that the SERT can discover the necessary logical processor and memory information needed to run the tool. Highly desired, but not required: Test and assist with enhancement of discovery routines to automate discovery of much of the configuration for the new Environment.

Note that, in order to be effective in satisfying these commitments, the Environment Sponsor must be a member of SPEC and actively participate in the SPEC OSG Power subcommittee that manages the SERT. As discussed in Section 1.2, SPEC is a consortium with open membership (within the legal limits SPEC's not-for-profit incorporation).

Acceptance of some environments may require only a subset of the items listed in this section. For example, the new environment may be a new version of an operating system or a new distribution of an existing operating system or a hardware implementation that is related to one that is already accepted. These may only require a set of 5 tests for consistency, proof that discovery is working as intended, and one or two other spot checks. Environment owners must propose a limited acceptance process to the SPECpower Committee and be prepared to add tests to the plan if discussion warrants this.

#### 2.12.1. Test

Demonstrate that the SERT functions as expected and delivers realistic results for a specific configuration. The target configuration used for other environments has been a two-socket server with multiple disk drives and a moderate (32-128 GB) amount of memory. In case a SERT worklet does not function as expected, the environment sponsor works with the SERT development team to resolve the issue.

Demonstrate that the SERT scales as expected by running:

- On 1-socket, 2-socket, 4-socket, and 8-socket configurations (as supported by the environment).

- On at least 4GB, 8GB, 32GB, 128GB, and 1024GB of memory (as supported by the environment).

- With a single disk, 2 disks, 4 disks, and 8 disks (as supported by the environment).

- With processor cores of different frequencies.

- With memory of different speeds.

- With storage of different speeds.

- With five measurements of the full SERT suite on a single configuration to ensure that at least 4 of them complete without invalid messages for coefficient of variation (CV) or throughput targets, and that run-to-run variation also meets CV requirements.

- If the environment is expected to participate in multi-node measurements, it is highly recommended that a set of measurements be made in a multi-node environment, to ensure that measurements complete correctly and that cross-node CVs are satisfactory.

It is not required to measure every possible combination in the above list, but rather to cover the list in some combination. The following table is an example of a possible test matrix.

Environment owner/sponsors should be prepared to share the results of these tests on a SPEC-Confidential basis with the members of the SPEC OSG Power subcommittee. Results may be shared using actual performance values, or may be normalized to relative values that are consistent across the scope of measurements submitted for the acceptance proposal of the environment. However, other data may need to

| Full SERT<br>Suite  | System A – 1 socket<br>2.5 GHz<br>Measure on 4 GB and<br>8 GB memory with one<br>storage device | System B – 2 sockets<br>2.5 GHz<br>Measure five times on<br>128 GB memory with 4<br>storage devices | System C – 4 sockets<br>3.5 GHz<br>Measure on 32 GB and<br>1024 GB memory with<br>one storage device | System D – 8 sockets<br>2.2 GHz<br>Measure on 128 GB<br>memory with one<br>storage device |

|---------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Memory<br>tests     |                                                                                                 | Repeat full suite with<br>128 GB memory at<br>different speed than<br>prior runs                    |                                                                                                      |                                                                                           |

| Storage<br>tests    |                                                                                                 | Measure storage<br>workload on one<br>configuration with 1,<br>2, 4, 8 similar disks                | Measure storage<br>workload with 2 HDDs<br>and 2 SSDs                                                |                                                                                           |

| Processor<br>Speeds |                                                                                                 |                                                                                                     | Repeat Full Suite with<br>processor down-<br>clocked to 2.5 GHz                                      |                                                                                           |

| Second<br>JVM       | Repeat suite with 8 GB<br>of memory and one<br>storage device                                   | Measure five times on<br>128 GB memory with 4<br>storage devices                                    | Repeat Full Suite at<br>one of the prior<br>processor speeds                                         |                                                                                           |

be shared as a part of the owner/sponsor's ongoing commitment to participate in future development and testing.

Measurements in this matrix should be done using the tuning parameters identified for the environment. In particular, the 5 repeated measures require the use of final tuning parameters. Note that the above matrix is an example and is not the only allowable arrangement of tests.

# 2.12.2. Tuning Parameters

- Ensure that affinity tuning within SERT is operating properly for the target environment.

- Identify Java tuning parameters needed to obtain consistent measurement information that is comparable with other environments supported by the SERT.

- Identify requirements for setting huge pages for the environment, if appropriate

- Identify requirements for deactivating write cache for storage devices

# 2.12.3. Documentation

- Review existing documents, particularly this Design Document, the Users Guide and the Run and Reporting Rules

- Propose changes needed for each to accommodate the new environment

# 2.12.4. Ongoing Testing

- As minor changes are made to the SERT, primarily as a result of problem fixes, but perhaps with additional function, conduct a subset of the initial testing to ensure that the target environment has not been impacted.

- For significant changes to the SERT, such as the addition of new worklets, metric changes and alterations to the key functions of existing worklets, more extensive testing is required. This is particularly true if the changes make the operation of the SERT more restrictive in some way than prior versions.

#### 2.12.5. Technical Support

• Participate in the overall SERT technical support process. There will be questions that require the technical expertise of the SERT development team and the Environment Sponsor.

#### 2.12.6. Future Enhancements

- Work with the development team to enhance the SERT to include better discovery of the configuration tested in the target environment.

- Participate in the decision-making process regarding other possible enhancements, such as new worklets or modifications to existing worklets.

- Participate in the process for development and recommendation of future metrics associated with SERTbased measurements

- Test prospective changes to the SERT in the target environment to ensure that they function and perform as expected.

#### 2.12.7. Discovery

- Except for those components necessary to run the tool (logical processors, memory capacity), configuration discovery is not required to be complete, but can greatly enhance the ability to properly document a test result using the SERT.

- Work with the SERT development team to test and enhance discovery routines for the new environment.

# 2.13. Incremental Changes to Accepted Environments

In general, update enhancements to environments that already supported by an environment sponsor and accepted by the SPEC OSG Power committee are accepted with the existing parameters as specified by the environment sponsor. For example, an update to a processor offering that increases frequency or the number of cores per socket, but remains in the same named family as previously tested offerings is assumed to be supported using the same JVM and other tuning parameters as were previously specified. Similarly, update revisions to a JVM, operating system, or firmware are assumed to be accepted when the run parameters of the overall environment are not changed.

If update enhancements to any of the environment components cause the environment sponsor to alter the JVM and other tuning parameters from those previously specified, the updated environment becomes a new environment that requires at least some testing and related support commitments, as defined in Clause 2.12.

#### 2.13.1. Acceptance of Unannounced Products

Testing for unannounced processors, JVMs, or versions of software may be presented on a SPEC-Confidential basis to the OSG Power committee to facilitate rapid deployment of results from the SERT when the product is announced. All requirements documented in Clause 2.12 still hold. An official acceptance statement will not be made until the product announcement becomes public.

#### 2.13.2. Acceptance for Different Revisions of the SERT

Acceptance of an environment and associated environmental parameters for one revision of the SERT does not guarantee acceptance for either future or prior revisions. Additional testing for each revision may be required, as discussed in Clause 2.12.4. The level of testing required will be determined by the SPEC OSG Power committee, depending on the nature of the changes in the revision.

# 3. The SERT Architecture

# **3.1. Environment Overview**

The SERT is composed of multiple software components and shares design philosophies and elements from SPECpower\_ssj2008 in its overall architecture.

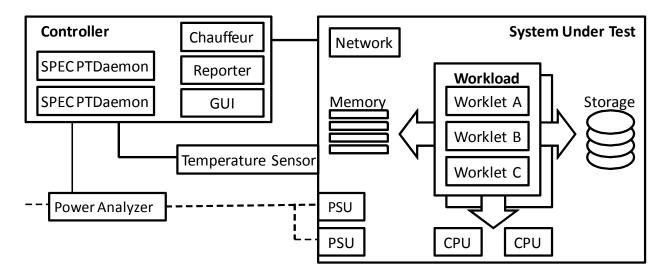

For the most basic SERT measurement setup the following is required:

- System under Test (HW) the actual system for which the measurements are being taken. The controller and SUT are connected to each other via a TCP/IP connection.

- Controller (HW, e.g. server, PC, laptop) the system to which the power and temperature sensor are connected. Multi-Controller environments are not supported.

- Power analyzer (HW) connected to the Controller and used to measure the power consumption of the SUT. Multiple Power Analyzer environments are supported.

- Temperature sensor (HW) connected to the Controller and used to measure the ambient temperature where the SUT is located.

- The SPEC PTDaemon (SW) connects to the power analyzer and temperature sensor and gathers their readings while the suite of workloads executes. All instances of the PTDaemon (each must be the same version) must run on the Controller, each listening on a different port.

- The Reporter (SW) summarizes the environmental, power, and performance data after a run is complete and compiles it into an easy to read format.

- The GUI (SW) eases configuring and executing the SERT suite.

# Figure 1: SERT System Diagram

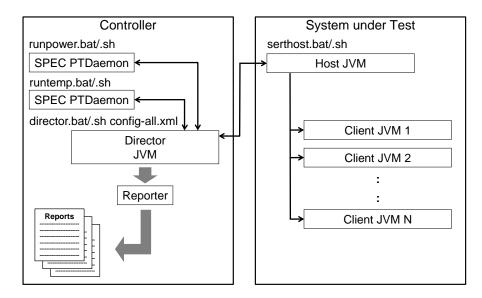

Chauffeur (SERT test harness) handles the logistical side of measuring and recording power data along with controlling the software installed on the SUT and Controller. It is responsible for the initialization of the following JVMs:

- The Client JVM executes the workload.

- The Host JVM starts all Client JVMs on one SUT.

- The Director instructs the Host JVM to start the workload.

The basic system overview in Figure 2: SERT Components shows these components in relationship to each other.

Figure 2: SERT Components

# 3.2. SERT Suite

The SERT Suite is composed of several logical elements including:

- User

- A User is a representation of an external agent that can initiate work (e.g. a human being).

- Each User may maintain identifying information (e.g. each User represents a Warehouse).

- $\circ~$  Each User may maintain temporary state information that persists from one transaction to another.

- Transaction

- A Transaction receives a User and transaction-specific Input as parameters.

- It produces some result.

- Some transactions may be able to verify their results this could be used for a small portion of transactions for auditing purposes.

- Worklet (Compress, CryptoAES, LU, SHA256, SOR, SORT, XMLValidate, Flood, Capacity, SSJ, Idle)

- A worklet defines a set of transactions that can be executed by a particular type of User.

- Scenario

- A Scenario is a group of one or more Transactions which are executed in sequence by a particular User.

- When a worklet is running a load level, each scenario is scheduled to being execution at a specific time. If that time is in the future, the User will execute no transactions until the scheduled time arrives.

- Each transaction in a scenario is submitted to a JVM-wide thread pool for execution.

- Interval

0

- o Each Interval includes pre-measurement, recording, and post-measurement periods.

- Transactions are executed throughout the entire interval, but results are only recorded during the recording period.

- $\circ$   $\quad$  Power consumption is recorded only during the recording period.

- Sequence

- A Sequence of related intervals.

- o The intervals in a sequence may be executed identically (e.g. during calibration).

- The intervals in a sequence may execute at different load levels (e.g. 100%, 80%, 60%, 40%, and 20% of the calibrated throughput).

- The intervals in a sequence may run with different configuration parameters (e.g. Capacity2 using a data store size of 4GB, 8GB, etc.).

- Phase

- A phase of execution: warm-up, calibration, or measurement

- Each phase consists of a sequence of intervals.

- Chauffeur supports multiple sequences in the measurement phase, but SERT always runs a single sequence in each phase.

- Workload (CPU, Memory, Storage, Hybrid, Idle)

- A workload is a group of worklets designed to stress some aspect of the SUT.

- $\circ$   $\;$  The worklets in each workload run one at a time in a defined order.

# 3.3. Workload

The design goal for the SERT suite is to include all major aspects of server architecture, thus avoiding any preference for specific architectural features which might make a server look good under one workload and show disadvantages with another workload. The SERT workload will take advantage of different server capabilities by using various load patterns, which are intended to stress all major components of a server uniformly.

The existing SPEC benchmarks are mainly based on tailored versions of real world applications representing a typical workload for one application area or a synthetic workload derived from the analysis of existing server implementations. These benchmarks are suitable to evaluate different sub-areas of the overall server performance or efficiency if power measurements are included. They are not designed to give a representative assessment of the overall server performance or efficiency.

It is highly unlikely that a single workload can be designed which achieves the goals outlined above, especially given the time constraints of the schedule targeted for the anticipated regulatory program. Therefore, the SERT workload will consist of several different worklets, each stressing specific capabilities of a server. This approach furthermore supports generating individual efficiency scores for the server components besides the overall system score.

# **3.4. Worklet Execution Phases**

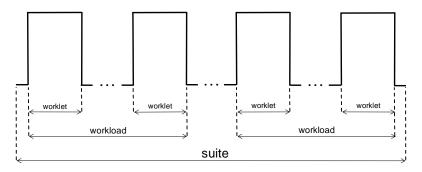

The SERT test suite consists of several workloads which are designed to stress the various components of the system under test (SUT): CPU, memory, and storage. Each workload includes one or more worklets which execute specific code sequences to focus on one of these system components. The overall design structure of the SERT is shown in Figure 3: SERT Suite Components.

#### Figure 3: SERT Suite Components

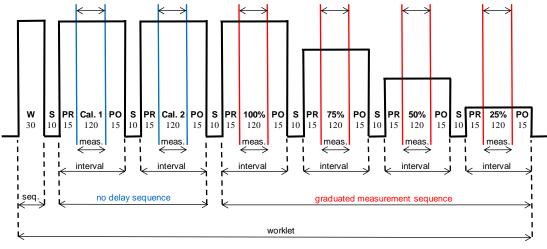

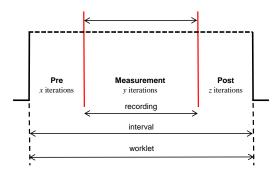

Worklets are run one at a time. Most worklets consist of a warm-up phase, a calibration phase, and a measurement phase; some worklets do not include warm-up or calibration. Each of these phases consists of a sequence of one or more intervals. Each interval includes a pre-measurement, recording, and post-measurement period. Score calculations are based on the number of transactions and the power consumed during the recording period only. All of the worklets other than Flood2 use fixed time periods for the pre-measurement, recording, and

post-measurement periods. The Flood2 worklet runs a fixed number of iterations for each period. The premeasurement period allows the worklet to reach steady state before recording begins. The pre- and postmeasurement periods also ensure that in multi-client and multi-host runs, all clients are executing transactions concurrently during the recording period, even if there are slight discrepancies in the time that the recording period begins and ends. Intervals are separated by short delays to summarize results and allow new power analyzer ranges to take effect.

Most worklets (with the exception of the memory and idle worklets) run as shown in Figure 4: Graduated Measurement Execution. Each of these worklets begins with a warm-up phase which runs transactions for a short period of time to allow the worklet execution to stabilize. Throughput during the warm-up interval may vary due to factors such as JIT compilation, memory allocation, and garbage collection, and system caches adjusting to the new load. After warm-up, a sequence of calibration intervals is run to identify the maximum rate that transactions can be executed for this worklet. Two calibration intervals are used, and the calibrated throughput is the average for these two intervals. After the calibrated throughput is found, SERT runs a series of intervals where the worklet is throttled back to run at some percentage of the maximum throughput. The series of load levels varies by worklet, as defined in Section 8.

W = Warm-up (30 sec) PR = Pre measurement (15 sec)

Cal. N = Calibration Interval N (120 sec)

S = Sleep (10 sec)

PO = Post measurement (15 sec)

nnn% = Measurement Interval (120 Sec)

**Figure 5: Fixed Iteration Execution**

Post = Post measurement (z iterations) (optional) Pre = Pre measurement (x iterations) (optional) Measurement = Measurement (y iterations) Worklet execution time = not fixed, depending on system capacity

# 4. Power and Temperature Measurements

The SERT provides the ability to automatically gather measurement data from accepted power analyzers and temperature sensors and integrate that data into the SERT result. It will be required that the analyzers and sensors must be supported by the measurement framework, and must be compliant with the specifications in this section.

# 4.1. Environmental Conditions

Power measurements need to be taken in an environment representative of the majority of usage environments. The intent is to discourage extreme environments that may artificially impact power consumption or performance of the server, before and during the SERT run.

The following environmental conditions need to be met:

- Ambient temperature lower limit: 20°C

- Ambient temperature upper limit: within documented operating specification of the SUT

- Elevation and Humidity: within documented operating specification of the SUT

- Overtly directing air flow in the vicinity of the measured equipment in a way that would be inconsistent with normal data center practices is not allowed.

# **4.2.** Temperature Sensor Specifications

Temperature must be measured no more than 50mm in front of (upwind of) the main airflow inlet of the SUT. To ensure comparability and repeatability of temperature measurements, SPEC requires the following attributes for the temperature measurement device used during the SERT run:

- Logging The sensor must have an interface that allows its measurements to be read by the SERT harness. The reading rate supported by the sensor must be at least four samples per minute.

- Accuracy Measurements must be reported by the sensor with an overall accuracy of +/- 0.5 degrees Celsius or better for the ranges measured during the SERT run.

# 4.3. Power Analyzer Requirements